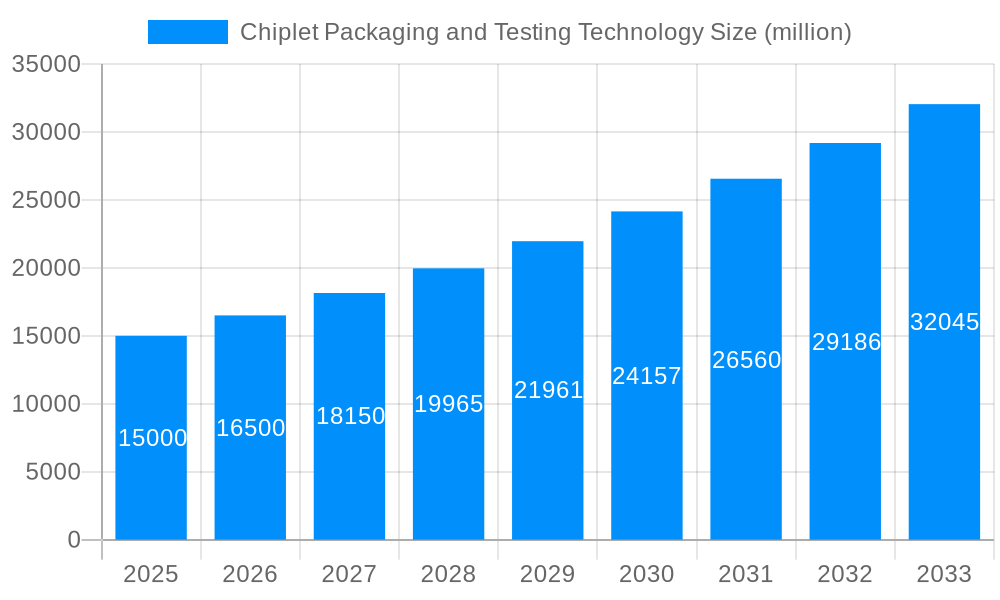

1. What is the projected Compound Annual Growth Rate (CAGR) of the Chiplet Packaging and Testing Technology?

The projected CAGR is approximately 11.15%.

Chiplet Packaging and Testing Technology

Chiplet Packaging and Testing TechnologyChiplet Packaging and Testing Technology by Type (/> 2D, 2.5D, 3D), by Application (/> Artificial Intelligence, Automotive Electronics, High performance Computing Devices, 5G Applications, Other), by North America (United States, Canada, Mexico), by South America (Brazil, Argentina, Rest of South America), by Europe (United Kingdom, Germany, France, Italy, Spain, Russia, Benelux, Nordics, Rest of Europe), by Middle East & Africa (Turkey, Israel, GCC, North Africa, South Africa, Rest of Middle East & Africa), by Asia Pacific (China, India, Japan, South Korea, ASEAN, Oceania, Rest of Asia Pacific) Forecast 2026-2034

MR Forecast provides premium market intelligence on deep technologies that can cause a high level of disruption in the market within the next few years. When it comes to doing market viability analyses for technologies at very early phases of development, MR Forecast is second to none. What sets us apart is our set of market estimates based on secondary research data, which in turn gets validated through primary research by key companies in the target market and other stakeholders. It only covers technologies pertaining to Healthcare, IT, big data analysis, block chain technology, Artificial Intelligence (AI), Machine Learning (ML), Internet of Things (IoT), Energy & Power, Automobile, Agriculture, Electronics, Chemical & Materials, Machinery & Equipment's, Consumer Goods, and many others at MR Forecast. Market: The market section introduces the industry to readers, including an overview, business dynamics, competitive benchmarking, and firms' profiles. This enables readers to make decisions on market entry, expansion, and exit in certain nations, regions, or worldwide. Application: We give painstaking attention to the study of every product and technology, along with its use case and user categories, under our research solutions. From here on, the process delivers accurate market estimates and forecasts apart from the best and most meaningful insights.

Products generically come under this phrase and may imply any number of goods, components, materials, technology, or any combination thereof. Any business that wants to push an innovative agenda needs data on product definitions, pricing analysis, benchmarking and roadmaps on technology, demand analysis, and patents. Our research papers contain all that and much more in a depth that makes them incredibly actionable. Products broadly encompass a wide range of goods, components, materials, technologies, or any combination thereof. For businesses aiming to advance an innovative agenda, access to comprehensive data on product definitions, pricing analysis, benchmarking, technological roadmaps, demand analysis, and patents is essential. Our research papers provide in-depth insights into these areas and more, equipping organizations with actionable information that can drive strategic decision-making and enhance competitive positioning in the market.

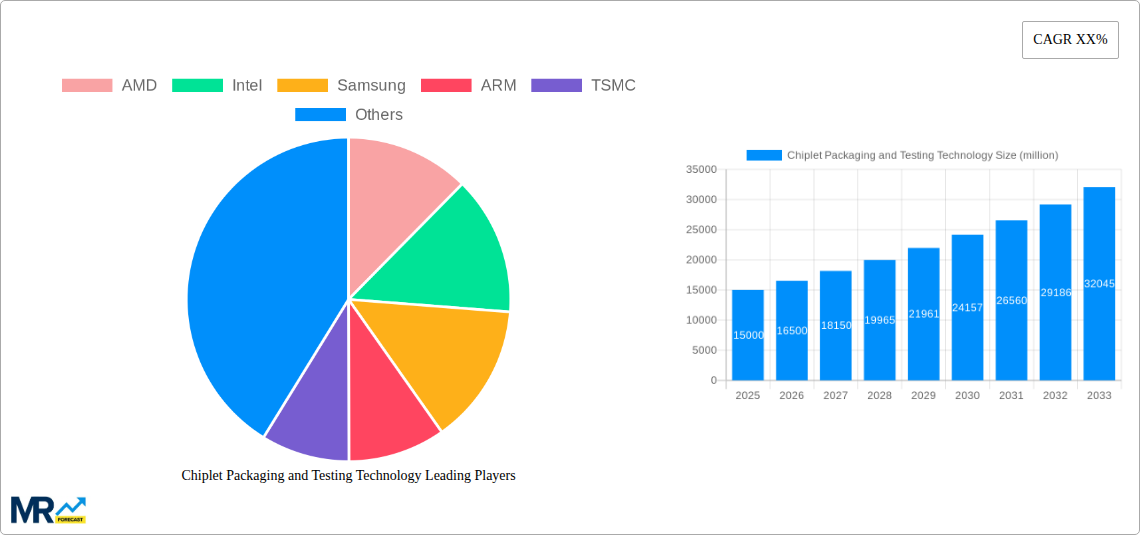

The Chiplet Packaging and Testing Technology market is experiencing robust growth, driven by the increasing demand for high-performance computing (HPC), artificial intelligence (AI), and 5G infrastructure. The market's expansion is fueled by the need for greater chip density, improved power efficiency, and faster processing speeds, all of which chiplets effectively deliver. Major players like AMD, Intel, and Nvidia are heavily invested in this technology, further accelerating its adoption. The industry is witnessing a shift towards advanced packaging techniques like 2.5D and 3D integration, enabling complex chiplet interconnections and enhanced performance. This trend is projected to continue, pushing the market towards substantial growth in the coming years. While challenges remain in terms of standardization and testing complexities, the overall outlook for chiplet packaging and testing remains exceptionally positive. The substantial investments in research and development from both established players and emerging companies indicate a confident market outlook with significant future potential. The market's segmentation reflects diverse applications, with substantial contributions from HPC, data centers, and mobile devices. The global market is geographically dispersed, with North America and Asia-Pacific representing key regions driving the overall growth.

The forecast period of 2025-2033 anticipates continued expansion, propelled by the rising adoption of chiplet technology in various sectors. This growth is estimated to be consistent with observed market trends and technological advancements. Further expansion will be driven by continued innovation in packaging materials, testing methodologies, and the development of new applications for chiplet technology in fields such as automotive electronics and high-bandwidth memory. The competitive landscape is dynamic, with numerous established players and emerging companies actively participating, leading to innovation and market consolidation. Despite potential economic fluctuations, the long-term prospects for chiplet packaging and testing remain positive, driven by the continuous demand for enhanced computing capabilities across multiple sectors.

The chiplet packaging and testing technology market is experiencing explosive growth, driven by the increasing demand for high-performance computing (HPC) and the limitations of monolithic chip designs. The market, estimated at $XX billion in 2025, is projected to reach $XXX billion by 2033, exhibiting a robust Compound Annual Growth Rate (CAGR) during the forecast period (2025-2033). This surge is fueled by the ability of chiplets to combine specialized dies with diverse functionalities, leading to enhanced performance, reduced costs, and accelerated time-to-market for advanced semiconductor products. Key market insights reveal a strong preference for advanced packaging techniques like 2.5D and 3D integration, which enable greater density and improved inter-die communication. The market is witnessing a significant shift towards heterogeneous integration, where chiplets with different functionalities (e.g., CPU, GPU, memory) are combined on a single substrate. This trend is particularly prominent in high-performance computing, artificial intelligence, and automotive applications. Furthermore, advancements in testing methodologies are crucial to ensure the reliability and performance of chiplet-based systems. Automated optical inspection (AOI) and advanced electrical testing techniques are becoming increasingly essential to guarantee the quality and functionality of these complex packages. The historical period (2019-2024) showcased the initial adoption of chiplet technology, with significant investments from major players like AMD, Intel, and TSMC laying the groundwork for the current exponential growth. The estimated market value for 2025 reflects the culmination of these early investments and the growing demand for chiplet-based solutions across various industries. The forecast period will likely witness substantial innovation in packaging materials, interconnection technologies, and testing methodologies further fueling market expansion. The market’s success hinges on the ability of companies to overcome the complexities associated with advanced packaging and testing, which involves challenges in thermal management, signal integrity, and yield optimization. This intricate interplay of technological advancement and market demand underscores the significant growth potential of the chiplet packaging and testing technology market.

Several factors are propelling the rapid expansion of the chiplet packaging and testing technology market. The primary driver is the relentless pursuit of higher performance and lower power consumption in electronic devices. Chiplet technology allows for the integration of specialized high-performance dies, such as high-bandwidth memory (HBM) and custom accelerators, alongside more conventional processing units, resulting in significant performance improvements compared to monolithic chips. This advantage is particularly crucial for data centers, high-performance computing, and artificial intelligence applications, where computational demands are constantly increasing. Furthermore, the increasing complexity and cost of designing and manufacturing monolithic chips are pushing companies to explore the cost-effectiveness of chiplet-based solutions. By utilizing a modular approach, manufacturers can reduce the risk associated with complex monolithic designs, improve yield rates, and potentially lower overall production costs. This modularity also allows for easier updates and upgrades, as individual chiplets can be replaced or enhanced without requiring a complete redesign of the entire system. The rise of heterogeneous integration, where chiplets from different manufacturers with diverse capabilities are combined, is another key driver. This enables greater flexibility in system design and allows companies to leverage the best available technologies from various suppliers. Finally, substantial investments from major semiconductor companies and governments worldwide are accelerating the development and adoption of advanced packaging and testing technologies crucial for chiplet integration. These combined factors paint a clear picture of the positive momentum driving the explosive growth observed in the chiplet packaging and testing market.

Despite the significant growth potential, the chiplet packaging and testing technology market faces several challenges and restraints. One of the primary hurdles is the complexity of designing and manufacturing chiplet-based systems. Precise alignment and interconnection of multiple dies with different specifications require advanced manufacturing processes and rigorous quality control. Achieving optimal thermal management within a densely packaged system is another significant challenge, as the heat generated by high-performance chiplets needs to be effectively dissipated to prevent performance degradation and damage. The testing of chiplet-based systems is inherently more complex than monolithic chips. Ensuring the seamless interaction and functionality of multiple dies requires sophisticated testing methodologies and equipment. Furthermore, the cost of advanced packaging and testing equipment can be substantial, making it a barrier to entry for smaller companies. The need for specialized expertise and skilled labor adds to the overall cost and complexity. Interoperability challenges between chiplets from different manufacturers can also hamper adoption. The development of standardized interfaces and protocols is crucial to ensure compatibility and facilitate the seamless integration of chiplets from diverse sources. Finally, the potential for intellectual property (IP) disputes and security concerns related to the integration of third-party chiplets represent further significant restraints.

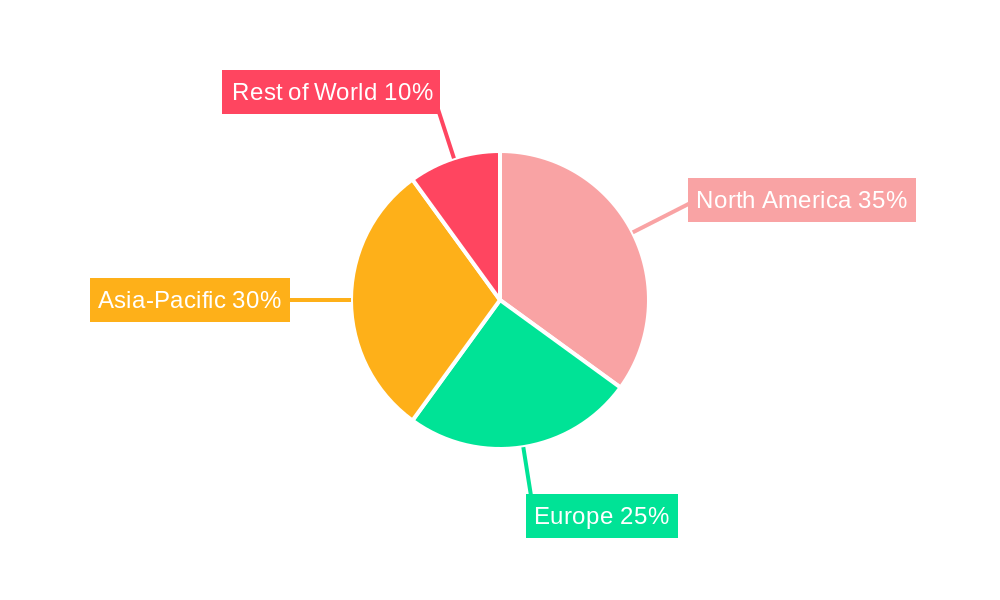

The chiplet packaging and testing technology market is geographically diverse, with significant growth anticipated across various regions. However, certain regions and segments are poised to dominate:

North America: This region is expected to lead the market due to the presence of major players like Intel, AMD, and Qualcomm, along with a strong emphasis on research and development in advanced semiconductor technologies. The substantial investment in data centers and high-performance computing infrastructure further fuels this dominance.

Asia-Pacific (specifically Taiwan, South Korea, and China): This region boasts prominent manufacturers like TSMC, Samsung, and numerous OSATs (outsourced semiconductor assembly and test) companies. Taiwan's expertise in advanced packaging and its role as a leading foundry are major drivers of growth. South Korea's strengths in memory and system-on-chip (SoC) technologies contribute significantly, while China's rapidly expanding semiconductor industry presents immense growth potential.

Europe: While smaller in overall market share compared to North America and Asia-Pacific, Europe is experiencing steady growth, driven by strong research and development in advanced semiconductor technologies and the presence of several key players.

Segments:

High-Performance Computing (HPC): This segment is a primary driver of growth due to the significant demand for high-performance computing solutions in data centers, artificial intelligence, and scientific research. The ability of chiplets to enhance performance and reduce power consumption makes them particularly suitable for HPC applications.

Artificial Intelligence (AI): The growing demand for advanced AI solutions is fueling the adoption of chiplets in machine learning and deep learning applications, where high processing power and efficiency are crucial.

Automotive: The increasing use of advanced driver-assistance systems (ADAS) and autonomous driving technologies is driving the adoption of chiplets in automotive applications. Their ability to combine diverse functionalities in a compact and efficient manner makes them ideal for automotive electronics.

5G and Mobile: The need for high-speed and low-latency communication in 5G networks is also propelling chiplet adoption. The demand for highly integrated and power-efficient solutions for mobile devices continues to fuel this segment's growth.

In summary, the combination of strong regional players and the overwhelming demand in segments like HPC and AI positions the market for substantial growth over the forecast period. The ongoing development of standardized interfaces and the continued miniaturization of components will further reinforce this trend.

Several factors are acting as catalysts for growth within the chiplet packaging and testing technology industry. Increased demand for higher performance and energy efficiency in electronics across various sectors, from high-performance computing to automotive, is a key driver. The cost-effectiveness of chiplet technology compared to monolithic solutions makes it particularly attractive to manufacturers. Government and industry investments in research and development are fostering innovation in packaging and testing techniques, further accelerating the adoption of chiplets. The emergence of advanced packaging technologies, such as 3D stacking and heterogeneous integration, is opening up new possibilities for chiplet-based system design. These converging factors are creating a robust environment for continuous growth in this dynamic market.

This report provides a comprehensive overview of the chiplet packaging and testing technology market, covering market size and growth projections from 2019 to 2033. It analyzes key market trends, driving forces, challenges, and opportunities. The report identifies leading players and their market share, examines key regional and segment dynamics, and details significant developments in the sector. The insights provided are crucial for businesses involved in the semiconductor industry, enabling them to make informed strategic decisions in this rapidly evolving market. The detailed analysis of the historical period, the current market landscape, and future projections paints a complete picture of the chiplet packaging and testing technology industry, empowering stakeholders to navigate this complex and dynamic area successfully.

| Aspects | Details |

|---|---|

| Study Period | 2020-2034 |

| Base Year | 2025 |

| Estimated Year | 2026 |

| Forecast Period | 2026-2034 |

| Historical Period | 2020-2025 |

| Growth Rate | CAGR of 11.15% from 2020-2034 |

| Segmentation |

|

Note*: In applicable scenarios

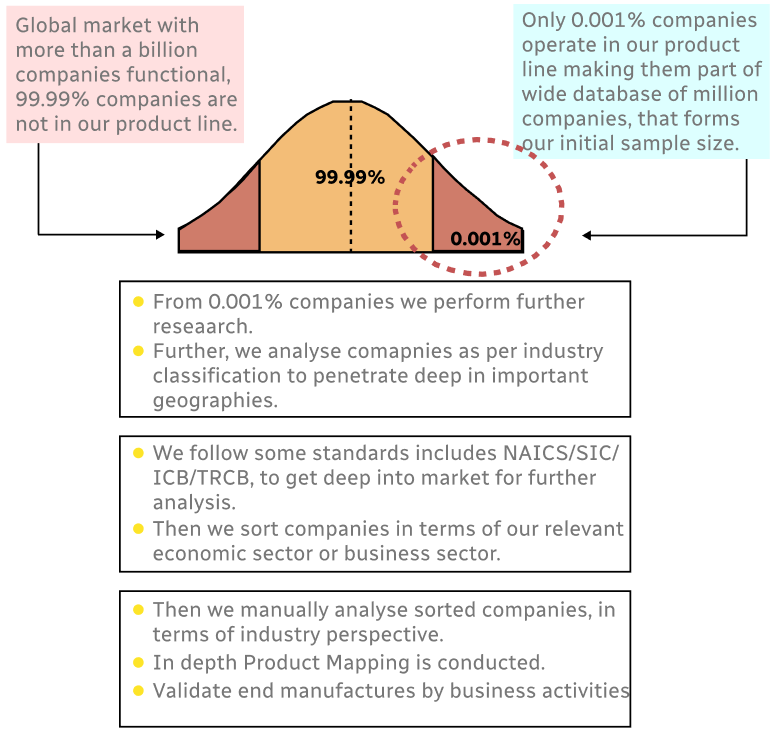

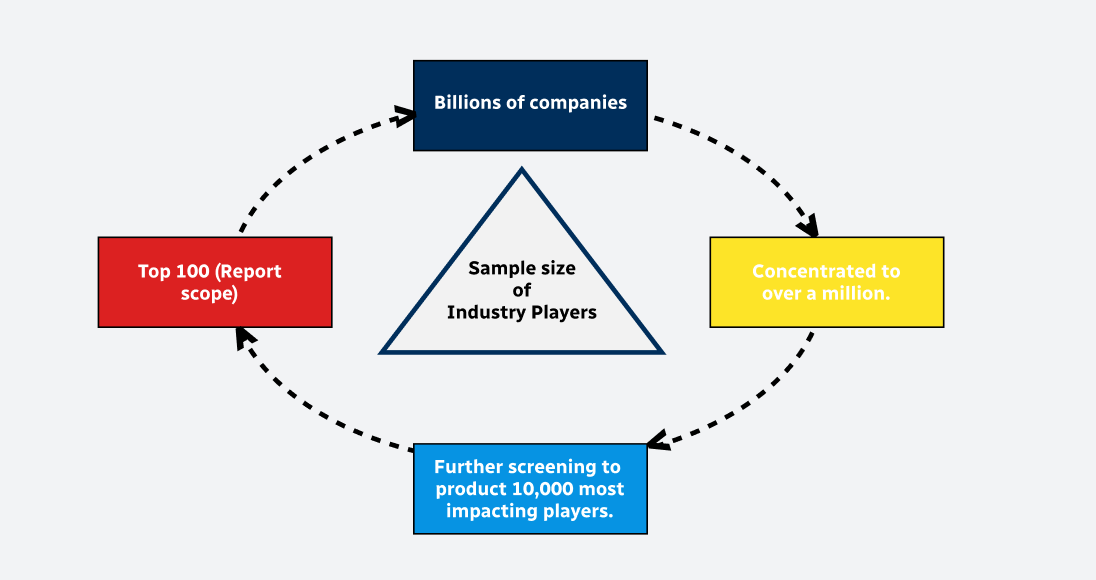

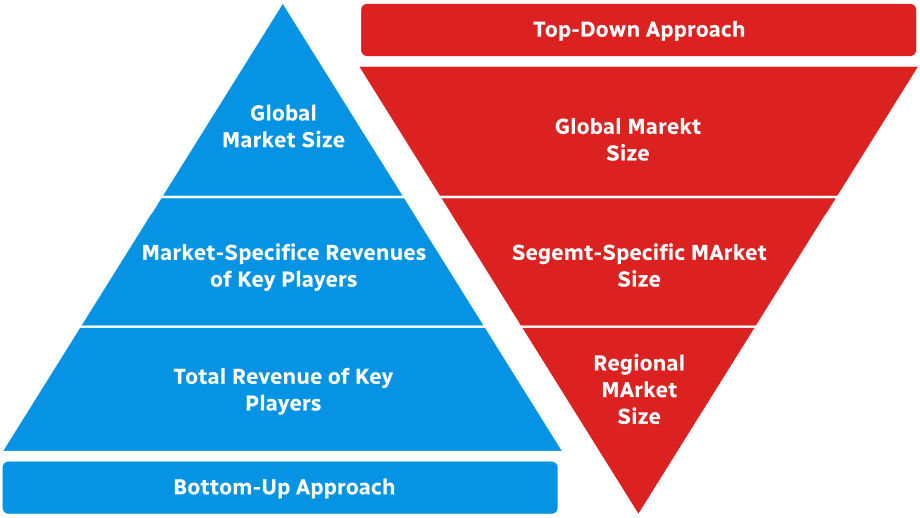

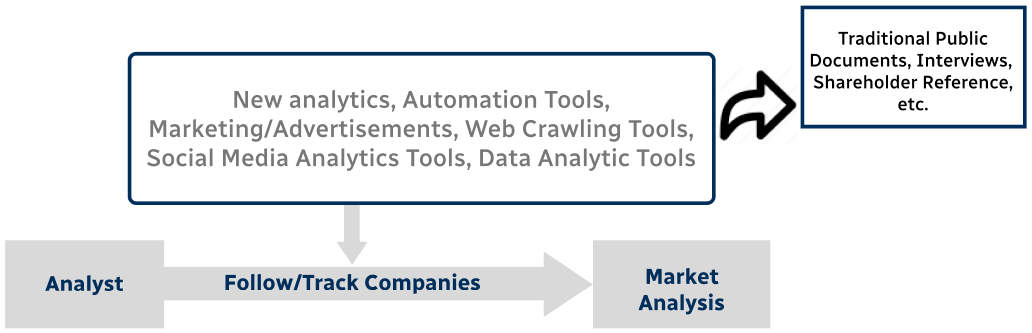

Primary Research

Secondary Research

Involves using different sources of information in order to increase the validity of a study

These sources are likely to be stakeholders in a program - participants, other researchers, program staff, other community members, and so on.

Then we put all data in single framework & apply various statistical tools to find out the dynamic on the market.

During the analysis stage, feedback from the stakeholder groups would be compared to determine areas of agreement as well as areas of divergence

The projected CAGR is approximately 11.15%.

Key companies in the market include AMD, Intel, Samsung, ARM, TSMC, ASE Group, Qualcomm, NVIDIA Corporation, Tongfu Microelectronics, VeriSilicon Holdings, Akrostar Technology, Xpeedic, JCET Group, Tianshui Huatian Technology, Forehope Electronic, Empyrean Technology, Tongling Trinity Technology.

The market segments include Type, Application.

The market size is estimated to be USD XXX N/A as of 2022.

N/A

N/A

N/A

N/A

Pricing options include single-user, multi-user, and enterprise licenses priced at USD 4480.00, USD 6720.00, and USD 8960.00 respectively.

The market size is provided in terms of value, measured in N/A.

Yes, the market keyword associated with the report is "Chiplet Packaging and Testing Technology," which aids in identifying and referencing the specific market segment covered.

The pricing options vary based on user requirements and access needs. Individual users may opt for single-user licenses, while businesses requiring broader access may choose multi-user or enterprise licenses for cost-effective access to the report.

While the report offers comprehensive insights, it's advisable to review the specific contents or supplementary materials provided to ascertain if additional resources or data are available.

To stay informed about further developments, trends, and reports in the Chiplet Packaging and Testing Technology, consider subscribing to industry newsletters, following relevant companies and organizations, or regularly checking reputable industry news sources and publications.